AMD, nell'architettura Zen 6 c'è anche un po' di Intel per modernizzare l'intera piattaforma x86

Le specifiche FRED rivoluzionano la gestione degli interrupt, migliorando le prestazioni.

[ZEUS News - www.zeusnews.it - 04-02-2026]

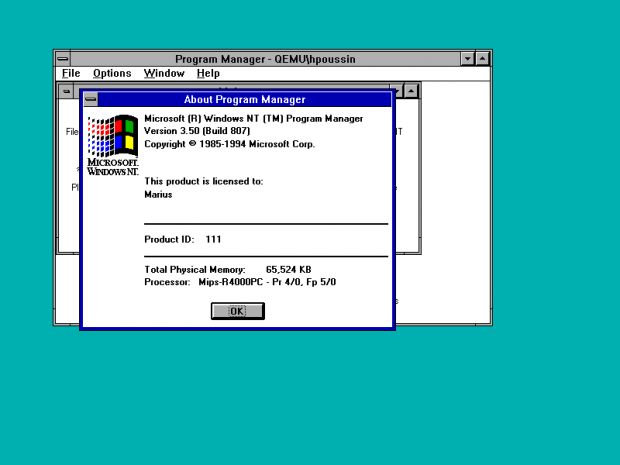

L'architettura Zen 6, alla base della prossima generazione di processori AMD, introdurrà un cambiamento profondo rispetto a Zen 5. La novità più rilevante riguarda l'adozione delle specifiche FRED (Flexible Return and Event Delivery), un meccanismo sviluppato da Intel per sostituire il sistema IDT di gestione degli interrupt utilizzato sin dagli anni '80. Questa decisione è stata presa proprio mentre anche Intel sta passando a FRED e indica un allineamento tecnico tra i due principali attori del settore, con l'obiettivo di modernizzare un componente fondamentale del funzionamento dei processori.

FRED è progettato per semplificare la gestione degli interrupt, riducendo la complessità delle transizioni tra user space e kernel. Introdotto con l'Intel 80286, l'IDT è rimasto sostanzialmente invariato per oltre quarant'anni, nonostante l'evoluzione delle architetture CPU. L'adozione di FRED permette di eliminare parte dell'eredità storica dell'architettura x86, migliorando la prevedibilità del comportamento del processore e riducendo la latenza nelle operazioni di sistema. L'adozione di FRED da parte di AMD è stata resa possibile grazie ai lavori dello x86 Ecosystem Advisory Group, un'iniziativa congiunta tra AMD e Intel finalizzata alla modernizzazione dell'architettura x86. L'obiettivo è ridurre la dipendenza da meccanismi obsoleti e migliorare la competitività rispetto alle architetture emergenti, in particolare ARM, che negli ultimi anni ha guadagnato terreno grazie a design più snelli e privi di vincoli storici.

Dal punto di vista tecnico, FRED introduce un modello più lineare per la gestione degli eventi, eliminando la necessità di passaggi intermedi e riducendo il numero di contesti da salvare e ripristinare durante un interrupt. Questo approccio consente di ridurre il tempo necessario per gestire eventi frequenti come input da periferiche, operazioni di rete o accessi al disco, con benefici diretti sulla reattività del sistema. Zen 6 introduce anche un nuovo design del CCD (Core Complex Die), il componente fisico che contiene i core della CPU. Le informazioni disponibili indicano un passaggio da 8 a 12 core per CCD, con una cache L3 unificata da 48 MB. Si tratta di un incremento del 50% rispetto alle generazioni precedenti, ottenuto grazie al processo produttivo TSMC N2 a 2 nanometri, che permette una maggiore densità senza aumentare significativamente le dimensioni del die. Il CCD Zen 6 dovrebbe misurare circa 76 mm², solo leggermente più grande dei CCD Zen 4 e Zen 5, ma con risorse interne molto più elevate.

Le modifiche architetturali includono anche ottimizzazioni per l'efficienza energetica. Il nodo TSMC N2 introduce transistor basati su tecnologia NanoSheet, che consentono un miglior controllo del canale e una riduzione delle perdite. Questo dovrebbe tradursi in un miglior rapporto prestazioni‑per‑Watt, un aspetto cruciale per server, workstation e sistemi ad alte prestazioni. Le prime analisi suggeriscono che Zen 6 offrirà un incremento dell'IPC (istruzioni per ciclo di clock) rispetto a Zen 5, anche se non sono ancora disponibili valori ufficiali. L'integrazione di nuove istruzioni e la modernizzazione del sistema di interrupt dovrebbero contribuire a migliorare le prestazioni in carichi di lavoro sensibili alla latenza e nelle applicazioni che fanno uso intensivo di operazioni di sistema.

Nonostante i cambiamenti profondi, Zen 6 manterrà la piena compatibilità con l'ecosistema x86 esistente. L'introduzione di FRED non richiede modifiche ai software attuali, poiché il nuovo meccanismo sostituisce l'IDT a livello hardware senza alterare le interfacce esposte ai sistemi operativi. Tuttavia, gli sviluppatori potranno beneficiare di un modello più semplice e prevedibile per la gestione degli interrupt. Le prospettive per Zen 6 indicano un lancio previsto nel corso di quest'anno, con varianti destinate sia al mercato consumer sia a quello server. Le versioni con V‑Cache 3D potrebbero arrivare successivamente, sfruttando la maggiore densità del nodo a 2 nm per incrementare ulteriormente la cache disponibile per core.

|

Se questo articolo ti è piaciuto e vuoi rimanere sempre informato con Zeus News

ti consigliamo di iscriverti alla Newsletter gratuita.

Inoltre puoi consigliare l'articolo utilizzando uno dei pulsanti qui

sotto, inserire un commento

(anche anonimo)

o segnalare un refuso.

© RIPRODUZIONE RISERVATA |

|

Intel pensiona i marchi Pentium e Celeron

AMD straccia Intel con i Ryzen 7000 e l'architettura Zen 4

Commenti all'articolo (2)

12-2-2026 18:41

5-2-2026 10:57

|

|

||

|

- Programmazione:

Evoluzione di carriera: da Sviluppatore IBM i a

PM/Tech Lead - Motori di ricerca:

I motori di ricerca privati - Al caffe' dell'Olimpo:

Topic personale - Linux:

Infloww su linux, si può? - Pc e notebook:

Caricare pc power bank - Aiuto per i forum / La Posta di Zeus / Regolamento:

Avvisi risposte e notifiche MP non mi arrivano - Sicurezza:

Account cloni Whats App - attenzione! - Al Caffe' Corretto:

btp valore - Pronto Soccorso Virus:

Sito insicuro e notifiche firefox - Dal processore al case:

info per scheda grafica che supporta OpenGL 4.5

Gladiator