DDR 6, sviluppo iniziato: prestazioni doppio rispetto a DDR 5 e integrazione di CAMM2

Chissà quanto costeranno.

[ZEUS News - www.zeusnews.it - 06-05-2026]

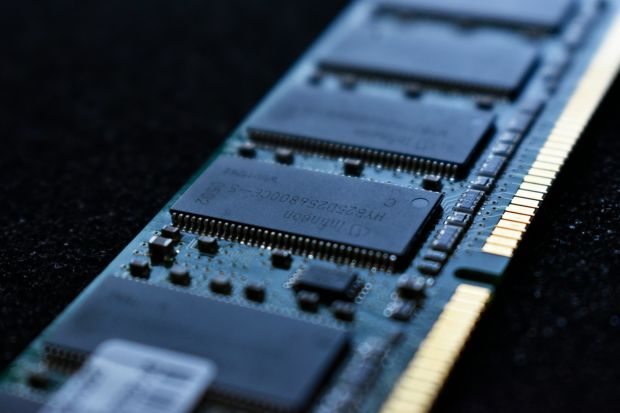

Samsung, SK Hynix e Micron hanno avviato lo sviluppo della memoria DDR 6, segnando l'inizio della prossima generazione di DRAM ad alta velocità. Le tre aziende hanno condiviso i primi design con i produttori di substrati, che stanno già realizzando prototipi e avviando i test di verifica. Le informazioni emergono da report industriali che indicano come la fase preliminare sia già in corso, nonostante il relativo standard JEDEC non sia ancora stato finalizzato. Secondo le prime stime, DDR 6 offrirà un incremento significativo delle prestazioni rispetto a DDR 5, con velocità iniziali previste intorno a 8.800 MT/s e un potenziale massimo di 17.600 MT/s, pari al doppio dell'attuale limite ufficiale di DDR 5. Alcune implementazioni overclock potrebbero superare tali valori, raggiungendo fino a 21.000 MT/s secondo analisi tecniche preliminari.

La nuova architettura DDR 6 adotterà una struttura 4×24‑bit, in sostituzione del modello 2×32‑bit di DDR 5. Questo cambiamento è progettato per migliorare la parallelizzazione dei dati e la scalabilità della banda, ma introduce complessità aggiuntive nella gestione dell'integrità del segnale, soprattutto alle frequenze più elevate. I produttori stanno collaborando con i partner di substrati per affrontare queste sfide fin dalle prime fasi. Lo sviluppo anticipato è motivato dalla crescente domanda di memoria ad alta banda nei datacenter dedicati all'intelligenza artificiale. DDR 5 rappresenta già oltre l'80% delle spedizioni server e dovrebbe raggiungere il 90% entro la fine del 2026, mentre DDR 4 è in fase di progressivo abbandono. L'arrivo di DDR 6 è visto come un passo necessario per sostenere carichi di lavoro sempre più intensivi.

La collaborazione tra produttori di DRAM e fornitori di substrati è iniziata più di due anni prima della prevista introduzione commerciale, come avviene tipicamente per le nuove generazioni di memoria. Le aziende stanno definendo parametri come spessore dei moduli, stack‑up, routing e limiti di potenza, in attesa che JEDEC completi le specifiche definitive. Le prime bozze dello standard DDR 6 sono state pubblicate nel 2024, ma restano da definire elementi chiave come tensioni operative, pinout e standard dei segnali. La finalizzazione richiederà ulteriori revisioni, poiché le prestazioni previste richiedono un ripensamento dell'intero ecosistema hardware, dai controller di memoria alle schede madri.

Per superare i limiti fisici dei DIMM tradizionali, l'industria sta valutando l'adozione del formato CAMM2, che offre percorsi elettrici più brevi e una migliore gestione del rumore alle alte frequenze. Questo formato potrebbe diventare essenziale per supportare le velocità previste da DDR 6, soprattutto nei sistemi compatti. Le prime piattaforme a integrare DDR 6 saranno i server, come avviene per ogni nuova generazione di memoria. I notebook di fascia alta seguiranno una volta completata la validazione, mentre il mercato consumer dovrebbe adottare DDR 6 solo dopo il 2030, in linea con i cicli di transizione precedenti.

La produzione su larga scala non è attesa prima del 2028-2029, con una fase di validazione prevista per il 2027. La disponibilità per il mercato di massa dipenderà anche dall'andamento dei prezzi della DRAM, attualmente influenzati dalla forte domanda del settore IA.

|

Se questo articolo ti è piaciuto e vuoi rimanere sempre informato con Zeus News

ti consigliamo di iscriverti alla Newsletter gratuita.

Inoltre puoi consigliare l'articolo utilizzando uno dei pulsanti qui

sotto, inserire un commento

(anche anonimo)

o segnalare un refuso.

© RIPRODUZIONE RISERVATA |

|

Commenti all'articolo (0)

|

|

||

|

- Al caffe' dell'Olimpo:

[GIOCO] Associazioni di idee - Motori di ricerca:

I motori di ricerca & la privacy - Tablet e smartphone:

Utilizzo smartphone - Internet - generale:

Come interagite con la IA? - Aiuto per i forum / La Posta di Zeus / Regolamento:

Avvisi risposte e notifiche MP non mi arrivano - Altra ferraglia stand-alone:

Android TV e smart TV - Sicurezza:

Abbonamento ad antivirus con prova gratuita - Programmazione:

Evoluzione di carriera: da Sviluppatore IBM i a

PM/Tech Lead - Windows 11, 10:

Comparsa di un Disco Locale sconosciuto - Linux:

Infloww su linux, si può?